Страница: 8/10

После обнуления на выходе “окончание счета” СВВ и следовательно, на входе 1 DD1 устанавливается логическая единица, если конденсатор С1 заряжен а клавиша «Сброс» не нажата то схема перейдет в режим ожидания. На выходе “сброс СВВ” установится логический ноль разрешающий его работу. Конденсаторы С2 и С3 предназначены для предотвращения ложного срабатывания схемы из – за помех. Их емкость должны относиться между собой как (50 – 100) * С3 = С2, а максимальная емкость С2 выбирается так, чтобы время ее зарядки не оказывало заметного влияния на точность интервала выдержки.

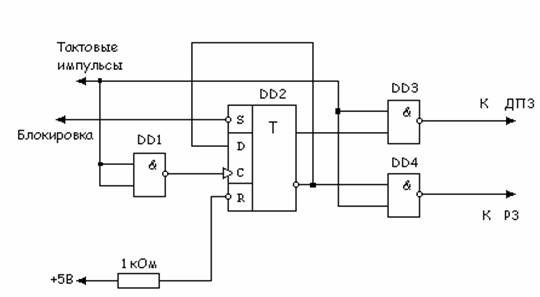

2) Схема управления

Принципиальная схема этого блока приведена на рис.

Он построен на одном из триггеров микросхемы К555ТМ2 и трех логических элементах микросхемы К555ЛА3. Характеристики этих микросхем были даны выше.

Блок предназначен для синхронного управления РЗ и ДПЗ. На вход “Тактовые импульсы” подаются импульсы с ТГ. Благодаря инвертору на элементе DD1 триггер переключается по спаду импульса.

Рис.

Для блокировки работы блока и следовательно окончания загрузки чисел с клавиатуры используется вход S триггера.

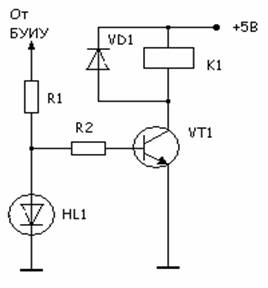

3) Исполнительное устройство.

Исполнительное устройство должно обеспечивать включение нагрузки на время выдержки или по прошествии этого времени. Принципиальная схема этого блока представлена на рис.

Рис.

Светодиод HL1 служит для индикации включения нагрузки. Помимо этого он, совместно с R1 выполняет роль делителя напряжения. С выхода этого делителя через резистор R2 напряжение подается на базу транзистора VT1 и открывает его. Резистор R2 ограничивает ток базы транзистора и, тем самым, предотвращает его влияние на БУИУ. Его сопротивление необходимо выбирать по возможности больше. В нашем случае оно было подобрано экспериментально и равно 10 кОм. В коллекторную цепь транзистора включается реле К1, которое своими контактами управляет нагрузкой. Диод VD1 необходим для замыкания токов самоиндукции, возникающих в обмотке реле при запирании транзистора. Тем самым он предотвращает пробой транзистора, а также возникновение помех по цепи питания микросхем. Сопротивление резистора R1 выбрано экспериментально, по приемлемой яркости свечения светодиода.

4) Блок управления исполнительным устройством.

Блок управления исполнительным устройством выполняет следующие функции:

включает исполнительное устройство в начале интервала выдержки

выключает исполнительное устройство после окончания выдержки

отключает исполнительное устройство при нажатии на клавишу «Сброс»

воспринимает нажатие на клавишу «Пуск» и подает сигнал управления на устройство блокировки.

Принципиальная схема этого блока приведена на рис.

Рис.

На триггере DD1 построено устройство управления схемой блокировки. Вход D триггера подключается к третьему разряду CH. После четырех нажатий клавиш сюда подается логический ноль, разрешающий запуск отсчета времени. К входу С подключается клавиша «Пуск» клавиатуры. Когда эта клавиша не нажата, на С установлен логический ноль благодаря резистору R1. При нажатии на клавишу «Пуск» перепад 0–1 на входе С разрешает запись информации (нуля) на выход триггера и, следовательно разрешает прохождение импульсов делителя частоты к СВВ.

Вход S подключается схеме обнуления параллельно входу обнуления СН. На элементах DD1 – DD5 собрано устройство контроля, управляющее нагрузкой. После включения устройства в сеть или нажатия на клавишу «Сброс» триггер DD5 устанавливается в нулевое состояние. На вход D при этом подается логическая единица. Эта единица также устанавливается и на одном из входов элемента DD2, выполняющего в данном случае электронного ключа. После разблокирования схемы блокировки первый перепад 0–1 появившийся на ее выходе, пройдет через элементы DD2, DD3 и диод VD2 на вход с триггера. Триггер переключится в единичное состояние и подаст логическую единицу на исполнительное устройство. Логический ноль с его инверсного выхода поступит на DD2 и запретит прохождение через него следующих импульсов. В этом состоянии устройство будет находится до окончания счета, либо до нажатия на клавишу “Сброс”. По окончании счета логический ноль с соответствующего выхода СВВ поступит на входы элемента DD4, играющего роль инвертора, и далее через VD1, на вход С триггера. Логический ноль со входа D перепишется на выход триггера и отключит исполнительное устройство. Элементы VD1, VD2 и R2 представляют собой простейший логический элемент ИЛИ. Их применение позволило отказаться от микросхемы с элементами ИЛИ и обойтись имеющимися лишними элементами микросхемы К555ЛАЗ. Сопротивление резистора R2 подобрано экспериментально и равняется 2,7 кОм.

Реферат опубликован: 12/07/2006