Страница: 6/10

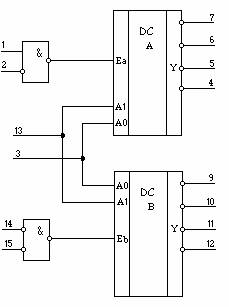

Микросхема К155ИД4 (рис. ) — два дешифратора, принимающих двухразрядный код адреса А0, А1. Дешифратор DC A имеет два входа разрешения: прямой Еа и инверсный Ёа, а дешифратор DC B — только инверсные входы разрешения дешифрации Еb.

Рис.

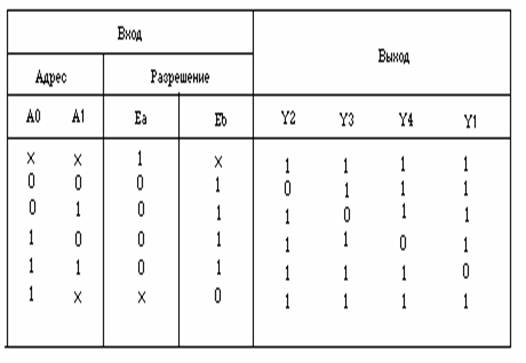

Если микросхема используется как демультиплексор, дешифратор DC A может принимать по входам Еа и Еа как прямой, так и инверсный адресные коды. Состояния для обоих дешифраторов как при дешифрации кода А0, А1, так и при демультиплексировании по адресу А0, А1 сведены в табл.

Табл.

Микросхема К555ИД4 потребляет ток 10 мА. Время задержки распространения сигнала от адресного входа А к выходу Y составляет 32 ns, время распространения от входа разрешения Е к выходу Y не превышает 30 ns для обоих вариантов исполнения.

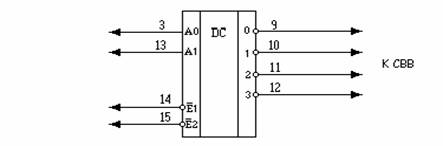

Принципиальная схема ДПЗ построенного на К555ИД4 приведена на рис.

Рис.

На входы А0 и А1 подается двоичное число произведенных нажатий клавиш от счетчика нажатий, а на входы Е1 и Е2 – сигналы разрешения от детектора нажатий и схемы управления. Выходы 0,1,2,3 подключаются к соответствующим разрядам счетчика выдержки времени.

Блоки отсчета выдержки

_

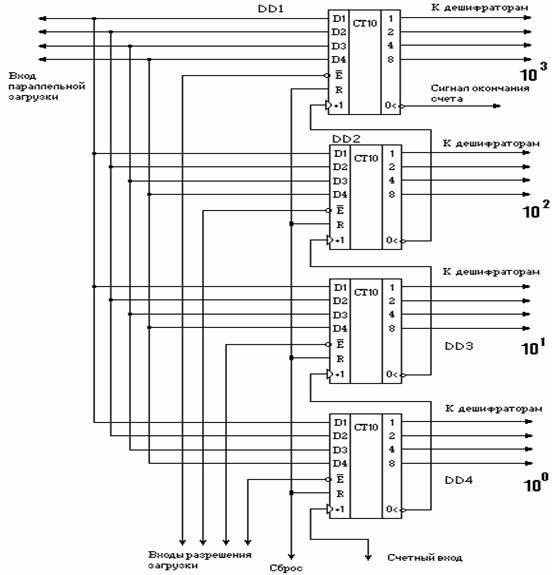

1) Счетчик выдержки времени

Счетчик выдержки времени является одним из основных узлов данного устройства. Он предназначен для подсчета количества поступающих от задающего генератора импульсов. Принципиальная схема счетчика приведена на рис. Счетчик работает в режиме вычитания – из заданного первоначально количества импульсов с приходом очередного импульса вычитается единица. Когда счетчик полностью обнулится, на его выходе "<0" (МС DD1) появляется логический ноль, который, воздействуя на БУИУ, отключит нагрузку. Загрузка значений в счетчик производится параллельным способом, путем подачи соответствующего двоичного значения на входы D0 - D4, и логического нуля на один из входов разрешения загрузки Е.

Рис.

Тактовые импульсы подаются на счетный вход +1 микросхемы DD4. Блок дешифраторов подключается к выводам 1-2-4-8 каждой из микросхем.

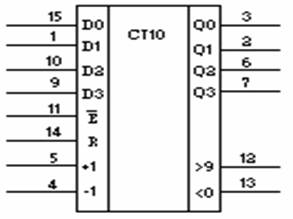

Для построения счетчика была использована микросхема К555ИЕ6, что позволило обойтись всего четырьмя микросхемами без каких либо дополнительных элементов. Цоколевка микросхемы показана на рис.

Рис.

Микросхема представляет собой реверсивный двоично-десятичный счетчик. Импульсные тактовые входы для счета на увеличение +1 (вывод 5) и на уменьшение -1 (вывод 4) в этой микросхеме раздельные. Состояние счетчика меняется по положительным перепадам тактовых импульсов от низкого уровня к высокому на каждом из этих тактовых входов.

Для упрощения построения счетчиков с числом разрядов, превышающих четыре, микросхема имеет выводы окончания счета на увеличение (">9", вывод 12) и на уменьшение ("<0", вывод 13). От этих выводов берутся тактовые сигналы переноса и заема для последующего и от предыдущего четырехразрядного счетчика. Дополнительной логики при последовательном соединении этих счетчиков не требуется: выводы ">9" и "<0" предыдущей микросхемы присоединяются к выводам "+1" и "-1" последующей. По входам разрешения параллельной загрузки РЕ и сброса R запрещается действие тактовой последовательности и даются команды загрузки четырехразрядного кода в счетчик или его сброса.

Если на вход "–1" подается импульсный перепад от низкого уровня к высокому, от содержимого счетчика вычитается 1. Аналогичный перепад, поданный на вход +1, увеличивает счет на 1. Если для счета используется один из этих входов, на другом тактовом входе следует зафиксировать напряжение высокого логического уровня. Первый триггер счетчика не может переключиться, если на его тактовом входе зафиксировано напряжение низкого уровня. Во избежание ошибок менять направление счета следует в моменты, когда запускающий тактовый импульс перешел на высокий уровень, т. е. во время плоской вершины импульса.

На выходах ">9" и "<0" нормальный уровень—высокий. Если счет достиг максимума (цифра 9), с приходом следующего тактового перепада от высокого уровня к низкому на вход +1 (более 9) на выходе ">9" появится напряжение низкого уровня. После возврата напряжения на тактовом входе "+1" к высокому уровню, напряжение на выходе ">9" останется низким еще на время, соответствующее двойной задержке переключения логического элемента ТТЛ.

Аналогично на выходе "<0" появляется напряжение низкого уровня, если на вход "-1" пришел счетный перепад низкого уровня. Импульсные перепады от выходов ">9" и "<0" служат, таким образом, как тактовые для последующих входов "+1" и "-1" при конструировании счетчиков более высокого порядка. Такие многокаскадные соединения счетчиков ИЕ6 не полностью синхронные, поскольку на последующую микросхему тактовый импульс передается с двойной задержкой переключения.

Реферат опубликован: 12/07/2006